# NEW RELEASE LTEC Corporation Your most experienced partner in IP protection

SiC MOSFET(1200V): SemiQ Gen3 GP3T040A120H 概要、

構造解析レポート

パッケージ

SiC MOSFETチップ

### レポート概要

SemiOから最新の第3世代SiC MOSFETが発表されました。この第3世代の製品は、第2世代 と比較してチップサイズの縮小に加えて、 RonxAAなどの性能向上がなされており、EV充電 ステーション、太陽光発電インバータ、産業用電源など、幅広い市場をターゲットとしています。 今回、この第3世代の概要解析、構造解析レポートをリリースしました。概要解析では同社製 第2世代品(2022年)と、構造解析ではそれに加え、他社製品との構造的な比較を行っています。

※ 第2世代 SiC MOSFET GP2T040A120Hの解析レポート(22G-0047-1)は販売中です。 エルテックまでお問い合わせください。

#### 製品特徴

型番: GP3T040A120H  $V_{DS}$ =1200V、 $I_{D}$ =62A、 $R_{DS(ON)}$ =38m $\Omega$  製品リリース日:2025年2月

データシート: https://semig.com/wp-content/uploads/2025/02/GP3T040A120H.pdf

第2世代からの変更点

- ・第3世代SiC MOSFETはセルレイアウトの変更。チップサイズが27%縮小化。

- ・高密度MOSFETチャネルと単位面積あたりのオン抵抗指標 (RonxAA) の低減。

### 解析内容&レポート価格

- ① 概要解析レポート 価格 ¥300,000(税別) 発注後1weekで納品

- ・第3世代品は第2世代品と比べて、チップサイズが27%縮小化していますが、Ronは同程度。 特徴的な平面レイアウトに変更することによってRonAAを低減しています。

- ② 構造解析レポート 価格 ¥600,000(税別) 発注後1weekで納品

- ・トランジスタの平面セルレイアウトは、同社や他メーカーには見られないような 形状となっています。そのため、複数方向から断面を観察してGate形状、注入構造を 観察しています。

- ・チップ外周部領域の耐圧構造についても平面、断面から特徴を確認しています。

#### ①概要解析レポート 目次

| 【目次】                                   | Page  |  |  |

|----------------------------------------|-------|--|--|

| 1 デバイスサマリー                             |       |  |  |

| Table1-1:デバイスサマリー・・・・                  | 3     |  |  |

| 1-1. 解析結果まとめ                           |       |  |  |

| Table1-2: デバイス構造:SiC MOSFET            |       |  |  |

| Table1-3: デバイス構造:レイヤー材料・膜厚             | 4-5   |  |  |

| 2 パッケージ観察                              |       |  |  |

| 2-1. 外観観察 ・・・・                         | 7     |  |  |

| 3 SiC MOSFETチップ概要解析                    |       |  |  |

| 3-1. 平面概要解析(OM) (チップ観察) ・・・            | 9     |  |  |

| 3-2. セル部 断面概要解析 (Epi膜厚・セルピッチ確認)    ・・・ | 10-11 |  |  |

| 3-3. 外周部 断面概要解析 (耐圧構造確認) ・・・           | 12    |  |  |

| 4 同社製前世代品との比較・・・・                      | 14-15 |  |  |

#### ②構造解析レポート 目次

|      | 次】                                                        |       | Page     |

|------|-----------------------------------------------------------|-------|----------|

| 1    | デバイスサマリー                                                  |       | 1 480    |

| ı    | Table1-1:デバイスサマリー                                         |       | 3        |

| 1-1. |                                                           |       | 3<br>4-5 |

| 1-1. | Pが相来まとめ<br>Table1-2: デバイス構造:SiC MOSFET                    |       | 4-5<br>6 |

|      | Table1-3: デバイス構造・SiC MOSFET<br>Table1-3: デバイス構造:レイヤー材料・膜厚 |       | 7        |

|      |                                                           |       | 8        |

| 2    | Table1-4: デバイス構造:実装パッケージ構造概要                              | • • • | <u> </u> |

| _    | パッケージ解析                                                   |       | 10 11    |

| 2-1. |                                                           | • • • | 10-11    |

| 2-2. |                                                           |       | 12       |

| 2-3. | パッケージ断面構造解析                                               |       | 13-24    |

| 3    | SiC MOSFETチップ構造解析                                         |       |          |

| 3-1. | 平面構造解析(OM)                                                |       | 26-39    |

| 3-2. | 平面構造解析(SEM)                                               |       | 40-47    |

| 3-3. | セル部 断面構造解析                                                |       | 48-60    |

| 3-4. | チップ外周部 断面構造解析                                             |       | 61-67    |

| 3-5. | Gate配線部 断面構造解析                                            |       | 68-71    |

| 4    | SiC MOSFETチップ裏面観察 (アニール痕)                                 |       | 73-74    |

| 5    | 他社製品および同社製前世代品との比較                                        |       |          |

| 5-1. | 他社製品との比較                                                  |       | 76       |

| 5-2. | 同社製前世代品との比較                                               |       | 77-81    |

|      |                                                           | •     | <u> </u> |

## ①概要解析レポートからの抜粋

|                                               | GP2T040A120H(Gen2) | GP3T040A120H (Gen3) |

|-----------------------------------------------|--------------------|---------------------|

| Die size A (mm x mm = mm²)                    |                    |                     |

| Transistor active area AA (mm²)               |                    |                     |

| Ron (Typ.) (m $\Omega$ ) / Vgs (V) @Tc = 25°C |                    |                     |

| Ron x AA (mΩ·mm²)                             |                    |                     |

|                   | GP2T040A120H(Gen2) | GP3T040A120H (Gen3) |

|-------------------|--------------------|---------------------|

| Cell plane layout |                    |                     |

| Cell pitch (µm)   |                    | ,                   |

前世代品との比較

# ②構造解析レポートからの抜粋

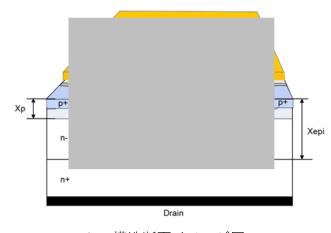

セル構造断面イメージ図

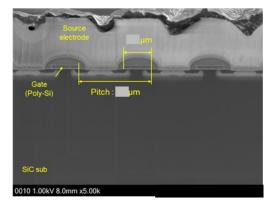

セル部断面SEM像

Source electrode

外周部断面SEM像