# NEW RELEASE LTEC Corporation Your most experienced partner in IP protection

SiC Cascode JFET (750V): onsemi Gen4 UJ4C075018KS 概要、構造解析レポート

パッケージ外観

SiC JFETチップ

### レポート概要

2025年1月、onsemiはQorvoの子会社United Silicon Carbide (UnitedSiC)を含むSiC JFET 事業を買収しており、onsemiのSiCパワー製品のラインナップを補完し、AIデータセンター 電源ユニットや電気自動車市場への拡大を狙っています。

SiC JFETは、チップ面積当たりのオン抵抗が低く高速スイッチング(~1MHz)が可能なことから AIデータセンターラック用電源の小型化および高効率化を実現できるデバイスとして世界大手の Infineon社もSiC JFET製品ファミリーを追加すると発表 (2025年 5月)しており、今後SiC JFET の動向を調査することは重要と捉えています。

今回解析対象であるUJ4C075018KSは、onsemi (Qorvo)の第4世代(現最新世代)の製品で、 特徴、詳細を明らかにするレポートをリリースしました。

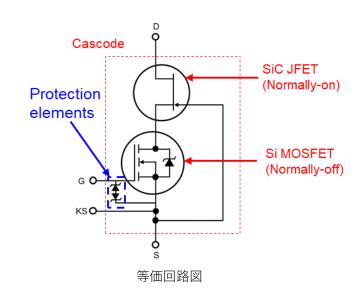

### 製品特徴

型番: UJ4C075018K4S  $V_{DS}$ =750V、 $I_{D}$ =120A、 $R_{DS(ON)}$ =18m $\Omega$ 、製品リリース日:2025年3月(データシート)

データシート: https://www.onsemi.jp/download/data-sheet/pdf/uj4c075018k4s-d.pdf

- ・第4世代ノーマリーオンSiC JFETトランジスタ

- ・アプリケーション: EV充電、スイッチング電源、PVインバータ等

# 解析内容&レポート価格

- ① 概要解析レポート: 価格 ¥400,000 (税別) 発注後1weekで納品

- ・JFETチップの面積当たりのオン抵抗は、一般的なSiC MOSFETの半分以下のRon x AAで あることを確認しました。

- ② 構造解析レポート: 価格 ¥700,000(税別) 発注後1weekで納品

- ・レポート①の内容を含みます。

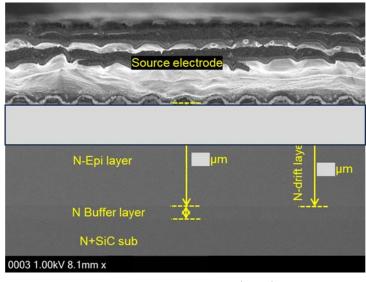

- ・本製品は縦型チャネルトレンチゲート構造です。同社製の前世代品との構造の比較の 結果、 セルピッチやチャネル長等約50%の縮小を確認しました。

- ・カスコード接続用のSiパワーMOSFETのセル断面構造解析を行なっています。

株式会社エルテック

mail contact2@ltec.biz

#### ① 概要解析レポート 目次

| 【目次】 |                            |  | Page  |

|------|----------------------------|--|-------|

| 1    | デバイスサマリー                   |  |       |

|      | Table1-1:デバイスサマリー          |  | 3     |

|      | 1-1. 解析結果まとめ               |  | 4     |

|      | Table1-2: デバイス構造:SiC JFET  |  | E     |

|      | Table1-3: デバイス構造:レイヤー材料・膜厚 |  | ິງ    |

| 2    | パッケージ観察                    |  |       |

|      | 2-1. 外観観察                  |  | 7     |

|      | 2-2. 内部レイアウト観察             |  | 8     |

| 3    | SiC JFETチップ概要解析            |  |       |

|      | 3-1. 平面概要解析(OM)            |  | 10    |

|      | 3-2. セル部 断面概要解析            |  | 11    |

|      | 3-3. チップ外周部 断面概要解析         |  | 12    |

| 4    | 前世代SiC JFETとの比較            |  | 13-14 |

#### ② 構造解析レポート 目次

| [ | 目次】                          |       | Page  |

|---|------------------------------|-------|-------|

| 1 | デバイスサマリー                     |       | _     |

|   | Table1-1:デバイスサマリー            |       | 4     |

|   | 1-1. 解析結果まとめ                 |       | 5     |

|   | Table1-2: デバイス構造:SiC JFET    |       | 6-7   |

|   | Table1-3: デバイス構造:Si MOSFET   |       | 8     |

|   | Table1-4: デバイス構造:実装パッケージ構造概要 |       | 9     |

| 2 | パッケージ解析                      |       |       |

|   | 2-1. 外観観察                    |       | 11-12 |

|   | 2-2. 内部レイアウト観察               |       | 13-14 |

|   | 2-3. パッケージ断面構造解析             |       | 15-41 |

| 3 | SiC JFETチップ構造解析              |       |       |

|   | 3-1. 平面構造解析(OM)              |       | 43-52 |

|   | 3-2. 平面構造解析(SEM)             |       | 53-57 |

|   | 3-3. セル部 断面構造解析              |       | 58-62 |

|   | 3-4. チップ外周部 断面構造解析           |       | 63-71 |

|   | 3-5. Gateパッド部 断面構造解析         |       | 72-75 |

| 4 | SiC JFETチップ裏面観察 (アニール痕)      |       | 76-78 |

| 5 | 前世代SiC JFETとの比較              | • • • | 79-81 |

| 6 | カスコード接続用Si MOSFET構造解析        |       | 82-87 |

|   |                              |       |       |

#### ① 概要解析レポートからの抜粋

## ② 構造解析レポートからの抜粋

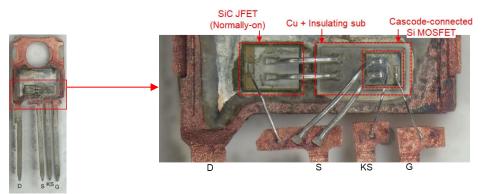

パッケージ内部レイアウト

SiC JFET セル断面構造 (SEM)