# New Release

## LTEC Corporation

Your most experienced partner in IP protection

IGBTパワーモジュール(1200V):Infineon HybridPACK DriveG2 FS520R12A8P1LB 搭載Si IGBT、FWD構造解析レポート

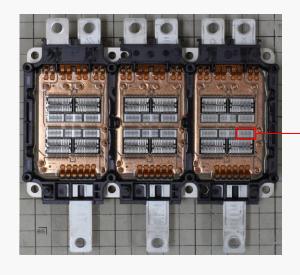

モジュール外観

モジュール内部

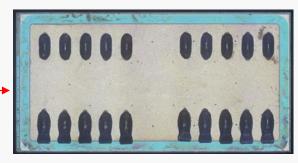

IGBT外観

#### <u>概要</u>

InfineonのHybridPACK Drive G2 型名:FS520R12A8P1LB(1200 V/520 A)は、6パック構成のパワーモジュールで、ハイブリッド車や電気自動車のトラクションモーター用インバータ向けに最適化されたモジュールです(2024年発売)

今回、同モジュールに搭載のIGBTおよびFWDについて、その詳細、特徴を明らかにした レポートをリリースしました。

#### <u>製品特徴</u>

型番: FS520R12A8P1LB V<sub>CES</sub>=1200V, I<sub>C</sub>=520A 製品リリース日: 2024年6月

データシート https://www.infineon.com/dgdl/Infineon-FS520R12A8P1LB-DataSheet-v01\_00-EN.pdf?fileId=8ac78c8c90530b3a0190b55f06126ef2

- •Infineon 1200V IGBT搭載 (750V品とはセル構造が異なります)

- •IGBTチップにオンチップ温度センサを内蔵

#### 解析内容

- ① 搭載Si IGBT構造解析レポート: 価格 ¥750,000 (税別) 発注後1weekで納品

- ・チップ上に温度センスダイオードが形成されており、極性の推定を実施しております。

- 本製品にはIGBT7より以前のプロセス技術が使用されていると推定しております。

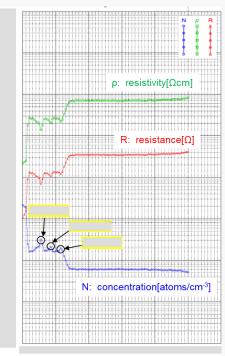

- ・裏面SR分析によりP+Collector層とN Field Stop層、N-Base層のキャリア濃度プロファイルを取得し チップの裏面側にピークがある事を確認しました。

- ② 搭載Si FWD構造解析レポート 価格 ¥ 500,000 (税別) 発注後1weekで納品

- ・Si FWDの平面レイアウト、ダイオードセル構造、終端部のJTE※構造を確認

- ・裏面SR分析によりN+層とN Field Stop層、N-Base層のキャリア濃度プロファイルを取得し、 チップの裏面側にピークがある事を確認しました。

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz

HP: https://www.ltec-biz.com/

Report No : 24G-0986-1,2 Release day: 2025.03.31

| 【目 次】               | Page  |

|---------------------|-------|

| 1 デバイスサマリー          |       |

| Table 1: デバイスサマリー   | • 3   |

| 1-1. 解析結果まとめ •••    | 4-6   |

| 2 モジュール解析           |       |

| 2-1. 外観観察           | 8-9   |

| 3 SiC MOSFETチップ構造解析 |       |

| 3-1. 平面構造解析 (OM)    | 11-29 |

| 3-2. 平面構造解析 (SEM)   | 30-34 |

| 3-3. セル部 断面構造解析     | 35-44 |

| 3-4 チップ外周部 断面構造解析   | 45-51 |

| 3-5 温度センスダイオード 構造解析 | 52-59 |

| 4 SR分析              | 61-64 |

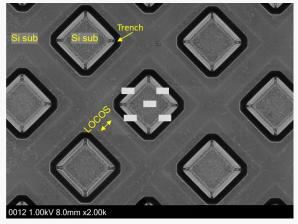

セル部 平面SEM像(Si基板レイヤ)

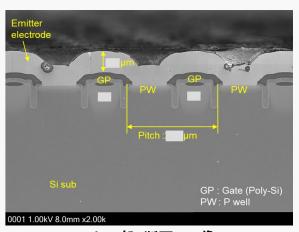

セル部 断面SEM像

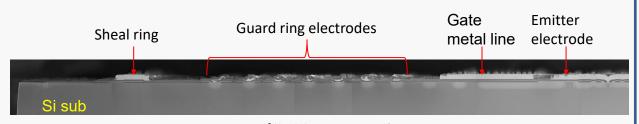

チップ終端部 断面SEM像

1049 1100kV 850mm x1010k 温度センスダイオード部 断面SEM像

Anode electrode

ILD

LOCOS

Temperature sense diode (Poly-Si)

Si sub

0049 1.00kV 8.0mm x10.0k

SR分析

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

| 【目次】                        | Page  |

|-----------------------------|-------|

| 1 デバイスサマリー                  |       |

| Table1-1:デバイスサマリー ・・・       | 3     |

| 1-1. 解析結果まとめ ・・・            | 4     |

| Table1-2: デバイス構造: Si FWD    | _     |

| Table1-3: デバイス構造: レイヤー材料・膜厚 | 5     |

|                             |       |

| 2-1. 外観観察 •••               | 8     |

| 3 Si FWDチップ構造解析             |       |

| 3-1. 平面構造解析(OM) •••         | 10-15 |

| 3-2. 平面構造解析(SEM) •••        | 16-17 |

| 3-3. 断面構造解析 •••             | 18-30 |

| 4 SR分析                      |       |

| 4-1. SR分析結果まとめ ···          | 32    |

| 4-2. SR分析箇所 •••             | 33    |

| 4-3. SR分析結果 •••             | 34-35 |

FWDチップ全体 (Top metal layer)

Anode electrode

Top Metal layer

Cross-section

Seal ring electrode

Cross-section

### チップ外周部 位置合わせ

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/