## New Release

### LTEC Corporation

Your most experienced partner in IP protection

SiCパワーモジュール (3300V): Infineon FF4000UXTR33T2M1 モジュール、SiC MOSFET構造解析レポート

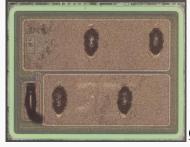

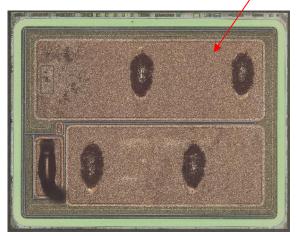

<u>チップ全体像</u> (Top metal layer)

### <u>概要</u>

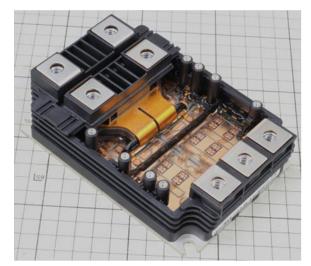

鉄道などのトラクションシステムの高効率化、太陽光、風力発電、蓄電システムの需要拡大により Infineonから高電圧、大電力用途向けに、XHP2 Cool SiC MOSFETハーフブリッジモジュール (3300V)がリリースされています。

今回、同モジュールの構造解析、搭載SiC MOSFETの構造解析を行い、同製品の構造とその特徴を明らかした下記2つのレポートをリリースしました。

#### 製品特徴

型番: FF4000UXTR33T2M1  $V_{DSS}$  = 3300V、 $I_{DN}$  = 500A、 $R_{DS(ON)}$  = 3.8m $\Omega$  製品リリース日: 2024年7月(データシート)

データシート:

$\underline{\text{https://www.infineon.com/dgdl/Infineon-FF4000UXTR33T2M1-DataSheet-v01\_00-JA.pdf?fileId=8ac78c8c93dda25b0194ca7eb93e2695}$

- •CoolSiC™ Trench MOSFET 内蔵

- ・アプリケーション: 鉄道輸送トラクションコンバータ、太陽光発電、蓄電システムなど

#### 解析内容、レポート価格

- ① モジュール構造解析レポート 価格 ¥1,150,000 (税別) 発注後1weekで納品

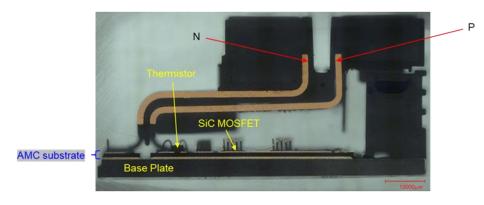

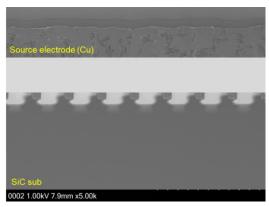

- ・ボンディングワイヤ、ソース電極部にはCuを使用。

- ・低熱抵抗 Rthを実現する同社特有のXT接合を使用。

- ・AIN系絶縁部材を用いたAMC基板が使用。

- ・AISiCベースプレートが使用。

- ② SiC MOSFET構造解析レポート 価格 ¥1,400,000 (税別) 発注後1weekで納品

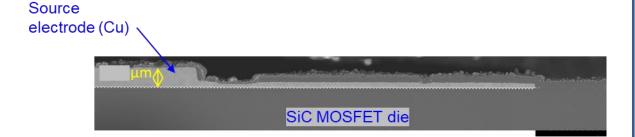

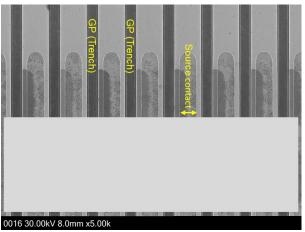

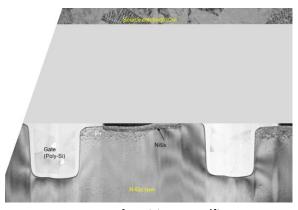

- •Source電極にCuを使用するための特殊な積層配線構造。

- ・高耐圧を実現するためのEpi層と終端構造。

- ※①②両レポート購入の場合は、合計から¥700,000引きにてご提供いたします。

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

> Report No: 24G-1094-1,2 Release day: 2025.03.31

# ① モジュール構造解析レポート 目次・解析内容

| 【目 次】                   | Page   |

|-------------------------|--------|

| 1 デバイスサマリー              |        |

| Table 1: デバイスサマリー ・・・   | 3      |

| 1-1. 解析結果まとめ •••        | 4      |

| Table 1-1:モジュール構造概要 ・・・ | 5      |

| 2 モジュール解析               |        |

| 2-1. 外観観察 •••           | 7-9    |

| 2-2. 内部レイアウト観察          | 10-13  |

| 2-3. 搭載チップ観察            | 14     |

|                         | 15- 38 |

| 3 ベースプレートの熱膨張係数         | 40- 41 |

#### 解析内容

・モジュール平面解析: モジュール外観観察、内部レイアウト確認

・モジュール断面解析: モジュール断面観察(OM・SEM)、材料分析(SEM-EDX)

# ① モジュール構造解析レポートからの抜粋

モジュール俯瞰像

| 番号  | 測定箇所                  | 測長 | 材料 |

|-----|-----------------------|----|----|

| 1   | 電源端子/GND端子            |    |    |

| 2   | SIC MOSFET            |    |    |

| 2-1 | ボンディングワイヤ<br>(Source) |    |    |

| 2-2 | ボンディングワイヤ<br>(Gate)   |    |    |

| 2-3 | 表面保護膜                 |    |    |

| 2-4 | 基板                    |    |    |

| 2-5 | 裏面電極-1                |    |    |

| 2-6 | 裏面電極-2                |    |    |

| 2-7 | 裏面電極-3                |    |    |

| 3   | ダイアタッチ                |    |    |

| 4   | AMC基板                 |    |    |

| 4-1 | AMC上部電極               |    |    |

| 4-2 | 絶縁基板                  |    |    |

| 4-3 | AMC下部電極               |    |    |

| 5   | はんだ                   |    |    |

| 6   | 冷却器                   |    |    |

| 6-1 | Niメッキ層                |    |    |

| 6-2 | AI/ME                 |    |    |

| 6-3 | ベースプレート               |    |    |

| 6-4 | AI/ME                 |    |    |

| 6-5 | Niメッキ層                |    |    |

| 7   | ケース                   |    |    |

モジュール断面構造概要

モジュール断面

SiC MOSFET パッド部断面SEM像

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

## ② SiC MOSFET構造解析レポート 目次・解析内容

| 【目 次】                                                  | Page          |

|--------------------------------------------------------|---------------|

| 1 デバイスサマリー                                             |               |

| Table 1: デバイスサマリー ・・                                   | • 3           |

| 1-1. 解析結果まとめ ・・                                        | <b>4</b> -6   |

| 2 モジュール解析                                              |               |

| 2-1. 外観観察                                              | <b>.</b> 8    |

| 2-2. 内部レイアウト観察                                         | • 9           |

| 3 SiC MOSFETチップ構造解析                                    |               |

| 3-1. 平面構造解析 (OM)                                       | <b>1</b> 1-28 |

| 3-2. 平面構造解析 (SEM) ••                                   | 29-42         |

| 3-3. セル部 断面構造解析                                        | 43-50         |

| 3-4 チップ外周部 断面構造解析 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | • 51-59       |

| 4 TEM解析 ··                                             | • 61-63       |

#### 解析内容

- チップ観察、測長

- ・SiC MOSFET平面解析: 配線接続、レイアウト確認

- •SiC MOSFET断面解析: チップ終端部、セル部 (エピ構造、膜厚の確認)

- •SiC MOSFET断面解析: セル部(TEM)

### ② SiC MOSFET構造解析レポートからの抜粋

厚膜のCu層

チップ全体像(Top metal layer)

セル部 平面SEM像(Poly-Si layer)

セル部 断面SEM像

セル部 断面TEM像

チップ終端部 断面SEM像