# New Release

### LTEC Corporation

Your most experienced partner in IP protection

SiC MOSFET (1200V): Navitas (GeneSiC) G3F34MT12K 概要、構造、 プロセス・電気特性解析レポート

<u>10-24</u>

TO-247-4 パッケージ

SiC MOSFETチップ

2024年6月、Navitas (GeneSiC: 2022年にNavitasが買収)は、新しい第3世代「高速G3F」MOSFET 650Vおよび1200Vファミリーを発表しました。G3Fの特徴として、構造面では独自の「トレンチアシストプレーナ」技術を採用、性能面では、優れた堅牢性(30%長い短絡耐量を実現)や最大600kHzのスイッチング速度が挙げられます。今回、この新しい第3世代1200V SiC MOSFETについて、過去に当社で解析したG3R品との比較を含め、デバイス構造の特徴を明らかにした概要、構造、プロセス・電気特性解析レポートをリリースしました(※1)。

(※1)リリースした2つのレポートの内容の違いにつきましては、P.3を参照ください。

### 製品特徴

概要

型番: G3F34MT12K Vdss=1200V、63A、34mΩ 製品リリース日: 2024年8月

Datasheet: https://navitassemi.com/wp-content/plugins/gb-navitas-stock-checker/product\_files/G3F34MT12K.pdf

- •自動車AEC-Q101認定

- ・アプリケーション: AIデータセンターの電源、xEV OBC&DC-DC、エネルギー貯蔵システムなど

### 解析結果(各レポートの解析内容はP.2,4,6を参照)

- ①概要解析レポート: 価格 ¥300,000(税別) 発注後1weekで納品

- ②構造解析レポート: 価格 ¥850,000(税別) 発注後1weekで納品

- ③プロセス・電気特性解析レポート: 価格 ¥750.000(税別) 発注後1weekで納品

- 本製品とNavitas製1200V SiC G3Rを比較した結果、本製品はG3Rより約15%低いRonxAAを 達成しています。

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8 e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

> Report No : 24G-0694-1,2,3 Release day: 2025.04.25

# ①概要解析レポート 目次

|   | 次】   |                                                 |       | Page |

|---|------|-------------------------------------------------|-------|------|

| 1 |      | デバイスサマリー                                        |       | -    |

|   |      | Table1-1:デバイスサマリー                               | • • • | 4    |

|   | 1-1. | 解析結果まとめ                                         | • • • | 5    |

|   |      | Table1-2: デバイス構造:SiC MOSFET                     |       | 6    |

|   |      | Table1-3: デバイス構造:レイヤー材料・膜厚                      | •••   | 0    |

| 2 |      | パッケージ解析                                         |       |      |

|   | 2-1. | 外観観察                                            | •••   | 8    |

| 3 |      | SiC MOSFETチップ構造解析                               |       |      |

|   | 3-1. | 平面構造解析(OM)                                      | • • • | 10   |

|   | 3-2. | セル部 断面構造解析                                      | • • • | 11   |

|   | 3-3. | 外周部 断面構造解析                                      | • • • | 12   |

| 4 |      | Navitas製Gen3 1200V SiC MOSFET(G3R75MT12K)との比較   |       | 14   |

| 5 |      | Appendix: About Trench Assist Planar Technology |       | 16   |

### ①概要解析レポートからの抜粋

概要、構造解析の目的は主に以下の3つです。

- 1)本製品の構造を明らかにする。

- 2)本製品と当社で過去に解析した同社製第三世代品(G3R)との構造の違いを知るため、比較を行う。

- 3)本製品で使用されている「トレンチアシストプレーナ」技術の詳細や背景・利点を明らかにするため、関連特許の調査を行う。

概要解析レポートと構造解析レポートは上記1)~3)について内容が異なります(下記表を参照。)

|    | 概要解析レポート内容<br>(24R-0694-1)                                 | 構造解析レポート内容<br>(24R-0694-2)                                |

|----|------------------------------------------------------------|-----------------------------------------------------------|

| 1) | ・チップ観察<br>・パッケージ観察<br>・SiC MOSFET断面解析: エピ層、セル部、チップ外周部(SEM) | 左の内容に加え、下記を行います。 ・パッケージ断面解析 ・SiC MOSFET平面解析: 配線接続、レイアウト確認 |

| 2) | ・G3Rとのチップサイズ、RonAAの比較                                      | ・左の内容に加え、G3Rとのセル断面構造、チップ外周部構造<br>の比較を行います。                |

| 3) | ・関連特許の調査はせず、<br>概要や図面の紹介をしています。                            | ・関連特許の概要や図面の紹介をしかつ調査を行います。                                |

#### 概要解析レポートと構造解析レポート(24G-0694-2)の内容の違い

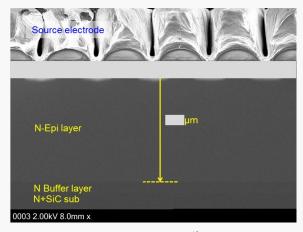

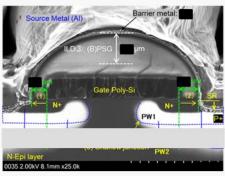

セル部 断面SEM像

|                                       |                  | G3R75MT12K | G3F34MT12K |

|---------------------------------------|------------------|------------|------------|

| ON resistance: RON                    | (mΩ) / Vgs (V)   | 75 / 15    | 34 / 18    |

| ON resistance per unit area<br>RONxAA | mΩ· mm²          |            |            |

| Die size                              | mm x mm<br>= mm² |            |            |

| Transistor active area AA             | mm <sup>2</sup>  |            |            |

| Cell source - source pitch, P         | μm               |            |            |

#### G3Rとの比較 (チップサイズなど)

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

# ②構造解析レポート 目次

|    | 次】                                              | Page      |

|----|-------------------------------------------------|-----------|

| 1  | デバイスサマリー                                        |           |

|    | Table1-1:デバイスサマリー                               | 3         |

|    | 1-1. 解析結果まとめ                                    | ••• 4     |

|    | Table1-2: デバイス構造:SiC MOSFET                     | ··· 5     |

|    | Table1-3: デバイス構造:レイヤー材料・膜厚                      | 6         |

| 2  | パッケージ解析                                         |           |

|    | 2-1. 外観観察                                       | ··· 8-9   |

|    | 2-2. 内部レイアウト観察                                  | ··· 10    |

| 3  | SiC MOSFETチップ構造解析                               |           |

|    | 3-1. 平面構造解析(OM)                                 | ··· 12-27 |

|    | 3-2. 平面構造解析(SEM)                                | ··· 28-33 |

|    | 3-3. セル部 断面構造解析                                 | ··· 34-43 |

|    | 3-4. 外周部 断面構造解析                                 | ••• 44-52 |

| _4 | SCM分析 (セル部)                                     | ··· 53-56 |

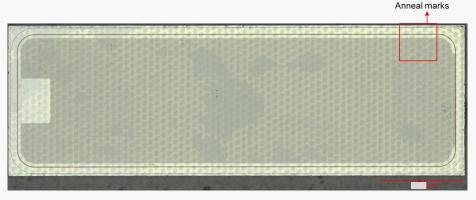

| 5  | SiC MOSFETチップ裏面構造解析 (アニール痕の解析)                  | ··· 57-59 |

| _6 | Navitas製 Gen3 1200V SiC MOSFET(G3R75MT12K)との比較  | 交 … 60-64 |

| 7  | Appendix: About Trench Assist Planar Technology | ••• 65-67 |

## ②構造解析レポートからの抜粋

SiC MOSFETチップ (SiC基板レイヤ)

G3F34MT12K

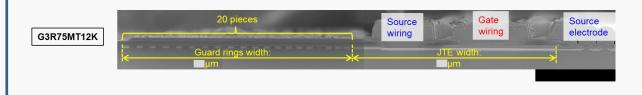

#### G3Rとの比較(チップ外周部構造)

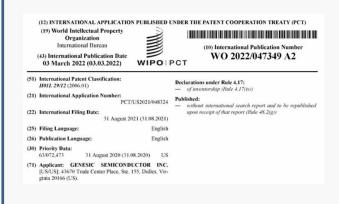

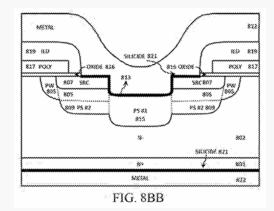

トレンチアシストプレーナ技術関連特許(WO2022047349A2) 概要・図面

株式会社エルテック Phone: 072-787- 7385 664-0845 兵庫県伊丹市東有岡4丁目42-8 e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/

# ③プロセス・電気特性解析レポート 目次

| 目次 |      |                                                           | Page  |

|----|------|-----------------------------------------------------------|-------|

| 1  |      | GeneSiC 3rd Gen SiC-MOSFET G3F34MT12K:<br>解析結果まとめ         | 3     |

|    | 1.1  | Table 1-1: GeneSiC 第3世代品と他社製SiC MOSFETsとの特性比較             | 4     |

|    | 1.2. | SiC-MOSFETチップ                                             | 5     |

|    | 1-3  | トランジスタアレーと チップ端部構成                                        | 6     |

|    | 1-4  | SiC MOSFETセル構造                                            | 7     |

|    |      | トランジスタの断面模式図                                              | 7     |

| 2  |      | SiC MOSFET 観察                                             | 8     |

|    | 2-1. | 構造解析(SEM)                                                 | 9     |

|    |      | トランジスタ構造とプロセス特徴 (1)-(6)                                   | 9-14  |

|    | 2-2  | チャネル長Lchを決定するためのN+およびPウェル形成プロセスの自己整合の詳細                   |       |

|    |      |                                                           | 15    |

|    |      | チャネル形成プロセスの詳細(推定)                                         | 15    |

|    | 2-4  | SiC MOSFET構成,レイアウト層とアライメントツリー                             | 16    |

| 3  |      | GeneSiC's SiC MOSFET G3F34MT12K解析結果の概要                    | 17    |

|    |      | Table 3-1:デバイス構造:SiC MOSFET                               | 18    |

|    |      | Table 3-2:デバイス構造: レイヤー材料・膜厚                               | 19    |

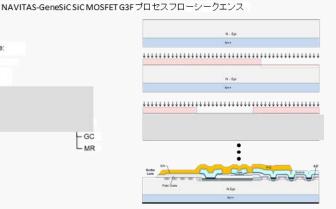

| 4  |      | 製造プロセスフロー解析                                               | 19    |

|    | 4-1. | SiCMOSFETのフロントエンドウェーハプロセスフロー(推定)                          | 20    |

|    | 4-2. | SiC MOSFETのプロセス・シーケンス断面図                                  | 21-24 |

| 5  |      | デバイス構造と電気特性解析                                             | 25    |

|    | 5-1. | Id-Vds 特性                                                 | 26    |

|    | 5-2. | デバイス温度をパラメータとしたオフ状態のドレイン電流(Idss)対ドレイン電圧(Vds)と活性化エネルギー(Ea) | 27    |

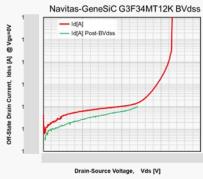

|    | 5-3. | オフ状態破壊電圧BVdss特性                                           | 28    |

|    | 5-4  | OFF状態ドレインリーク電流特性の比較                                       | 29    |

|    | 5-5. | ゲートリーク電流lgss特性                                            | 30    |

|    | 5-6. | ボディダイオード特性                                                | 31    |

|    | 5-7. | 容量(Ciss, Coss, Crss)-Vds特性                                | 32    |

|    | 5-8. | デバイス構造と電気特性解析:ON抵抗成分解析                                    | 33-35 |

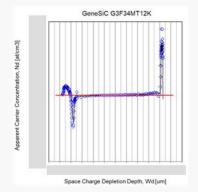

|    | 5-9  | N-エピ層不純物濃度解析                                              | 36    |

|    | 5-10 | デバイス構造と電気特性解析: ブレークダウン電圧                                  |       |

|    |      |                                                           | 37    |

| 6  |      | 関連文献目録                                                    | 38    |

| 7  |      | 関連特許目録                                                    | 38-41 |

# ③プロセス・電気特性解析レポートからの抜粋

Table 1: GeneSiC 1200V SiC MOSFET Comparison

| Maker               | Part no.        | Process<br>Gen. | Production | Die Size<br>mmxmm mm2 |      | Vdss<br>[V] | RON<br>[mΩ] | Intrinsic<br>RONxA<br>[mΩ·mm²] |

|---------------------|-----------------|-----------------|------------|-----------------------|------|-------------|-------------|--------------------------------|

| ROHM                | SCT3080KL       | Gen 3           | 2016       | 3.01 x 2.41           | 7.25 | 1200        | 80          | 408                            |

| CREE                | C2M0080120D     | Gen 2           | 2013       |                       |      |             |             |                                |

| WOLFSPEED<br>(CREE) | C3M0075120K     | Gen 3           | 2017       |                       |      |             |             |                                |

| INFINEON            | FF11MR12W1M1_B1 | Gen 1           | 2017       |                       |      |             |             |                                |

| STMicro             | SCT040N120G3AG  | Gen 3           | 2022       |                       |      |             |             |                                |

| Onsemi              | NTH4L040N120M3S | Gen 3           | 2022       |                       |      |             |             |                                |

| GeneSiC             | G3R75MT12K      | Gen 3           | 2020       |                       |      |             |             |                                |

| GeneSiC             | G3F34MT12K      | Gen 3           | 2024       |                       |      |             |             |                                |

Fig. 2-1-1 Transistor cell cross-sectional SEM image 1) CO-to-GP (Gate PolySi) misalignment. 3) nch) N+ ly mecnanical strain during nigh temperature excursions (Short-Circuit) conditions.

Fig.5-3-1 オフ状態破壊電圧BVdss

Fig.5-9-1(a) 深さ方向のキャリアドーピングプロファイル

Phone: 072-787- 7385 株式会社エルテック 664-0845 兵庫県伊丹市東有岡4丁目42-8

e-mail: contact2@ltec.biz HP: https://www.ltec-biz.com/