# New Release

### **LTEC Corporation**

Your most experienced partner in IP protection

# SiC MOSFET(1200V): SMC Diode Solutions S2M0080120D Overview and Structure Analysis Report

**Package**

SiC MOSFET die

#### **Overview**

SMC Diode Solutions is a US-funded semiconductor design and manufacturing company based in Nanjing, China, and started the operation of power discrete factory in Nanjing, in 2024 to strengthen sales of SiC devices in China. The company is a manufacturer that designs and manufactures discrete semiconductors, mainly diodes for consumer products. LTEC released the structure analysis report of its 1200V SiC MOSFET for automotive in order to understand its technological capabilities in automotive product.

#### Product features

- Product number: S2M0008120D  $V_{DSS}$  = 1200V,  $I_D$  = 41A,  $R_{DS}_{(on)}$  = 77m $\Omega$  Product release data: July 2023

- SMC's first generation SiC MOSFET.

- Application: EV fast charging module, EV on-board charger, solar inverter, DC-DC converter Report Contents (Please refer to P.2,3 for the table of contents of each report.)

- 1. Overview Analysis Report (12 pages)

- Observation of package and SiC MOSFET die, cross-section analysis of die cell and edge

- 2. Structure Analysis Report (68 pages)

- A very thin and flat die attach (Pb-based) is used.

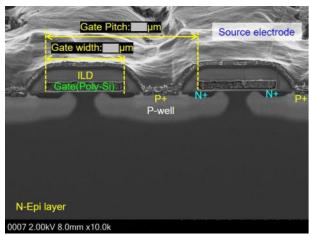

- The cell array has a planar gate structure.

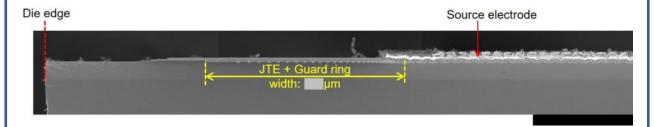

- A JTE and a guard ring (inside the JTE) are formed on the outer periphery of the die to reduce the electric field strength.

- Compared to the STMicro's 1200V SiC MOSFET, a major manufacturer, the performance (RonAA) is inferior, but it is comparable to the products from BASiC Semiconductor, a major Chinese manufacturer.

#### Report price

Delivered one week after order placement Please contact us for report pricing.

om/en/ Phone: +1-(650) 382-1181 Contact2@Itec.biz

> Report No : 23R-1005-1,2 Release day: 2024.06.21

# **Table of Contents of (1) Overview analysis report**

| [TA | BLE OF CONTENTS                                                    |       | Page |

|-----|--------------------------------------------------------------------|-------|------|

| 1   | Device summary                                                     |       |      |

|     | Table1-1: Device summary                                           |       | 3    |

|     | Table1-2: Device structure: SiC MOSFET                             | • • • | 5    |

| 2   | Package analysis                                                   |       |      |

|     | 2-1. Appearance observation                                        | • • • | 7    |

|     | 2-2. Mounted die observation                                       |       | 8    |

| 3   | SiC MOSFET die structure analysis                                  |       |      |

|     | 3-1. Plane structure analysis by Optical Microscope                |       | 10   |

|     | 3-2. Cross-sectional structure analysis of cell array              |       | 11   |

|     | 3-3. Cross-sectional structure analysis of the die outer periphery |       | 12   |

# **Table of Contents of (2) Structure analysis report**

| [TABLE OF CONTENTS]                                                |        |  |  |

|--------------------------------------------------------------------|--------|--|--|

| 1 Device summary                                                   |        |  |  |

| Table1-1: Device summary                                           | 3      |  |  |

| 1-1. Summary of analysis results                                   | ••• 4  |  |  |

| Table1-2: Device structure : SiC MOSFET                            | ··· 5  |  |  |

| Table1-3: Device structure: Layer material and thickness           | ••• 6  |  |  |

| Table1-4: Device structure: Package structure overview             | ••• 7  |  |  |

| 2 Package analysis                                                 |        |  |  |

| 2-1. Appearance observation                                        | ••• 9  |  |  |

| 2-2. Internal layout observation                                   | ••• 11 |  |  |

| 2-3. Mounted die observation                                       | ••• 12 |  |  |

| 2-4. Package cross-sectional structure analysis                    | ··· 13 |  |  |

| 3 SiC MOSFET die structure analysis                                |        |  |  |

| 3-1. Plane structure analysis by Optical Microscope                | ••• 26 |  |  |

| 3-2. Plane structure analysis by SEM                               | ••• 42 |  |  |

| 3-3. Cross-sectional structure analysis of cell array              | ••• 49 |  |  |

| 3-4. Cross-sectional structure analysis of the die outer periphery | ••• 57 |  |  |

| 3-5. Cross-sectional structure analysis of Gate electrode pad      | ••• 64 |  |  |

| 4 Comparison with other manufacturers' 1200V SiC MOSFETs           | ••• 68 |  |  |

### **Excerpt from (2) Structure analysis report**

Package cross-sectional structure

| Number | Measurement points      | Length measurement | Materials |

|--------|-------------------------|--------------------|-----------|

| 1      | Mold resin              |                    | 0.000     |

| 2      | Bonding wire            |                    |           |

| 2-1    | Gate                    |                    |           |

| 2-2    | Source                  |                    |           |

| 3      | SiC-MOSFET              |                    |           |

| 3-1    | Organic protective film |                    |           |

| 3-2    | Top metal               |                    |           |

| 3-3    | Substrate               | 0                  |           |

| 3-4    | Backside metal-1        |                    |           |

| 3-5    | Backside metal-2        | 9                  |           |

| 4      | Die attach              |                    |           |

| 5      | Die pad                 |                    |           |

| 5-1    | Die pad                 |                    |           |

| 5-2    | Plating layer           |                    | 9         |

Package cross-sectional structure overview

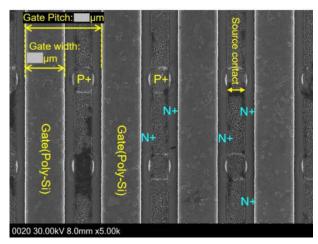

Plane SEM image of cell array (Poly-Si layer)

**Cross-sectional SEM image of cell array**

**Cross-sectional SEM image of the die outer periphery**