# New Release

### LTEC Corporation

Your most experienced partner in IP protection

# GaN SYSTEMS 100V GaN TRANSISTOR (GS61008T-E01-MR) STRUCTURE and PROCESS ANALYSIS REPORTS

**Dec 2019.** LTEC Corporation released detailed structure and process analysis reports of GaN Systems GaN power transistor (GS61008T-E01-MR)

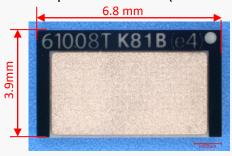

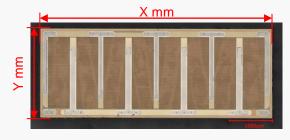

**Package**

Die image

#### **Product overview**

"GS61008T" is a normally-off GaN-on-Si power transistor with maximum operating voltage Vds = 100V and high current Ids = 90A made by GaN Systems. GaN Systems GS61008T offers the lowest input gate capacitance comparing to EPC GaN and Infineon Si-OPTIMOS transistors. And it is targeted for high current and ultra-short LIDAR pulsed applications.

#### Summary of the analysis results

- Lateral GaN HEMT (High Electron Mobility Transistor) realizes normally-off operation.

- The complex GaN-Epi layer structure.

- The breakdown voltage of the transistor is BVdss ~ 144V based on the measurement result

- The effective process technology node is extracted from the trench pitch and contact opening that are the minimum processing dimensions regarding the manufacturing process technology.

#### Report abstract

- The structural analysis report clarifies the details of GaN Systems' GaN power transistor "GS61008T-E01-MR", includes package appearance, X-ray observation, die plane analysis (wiring connection, layout), die cross section analysis (GaN transistor, die edge), GaN-Epi layer TEM-EDX analysis and electrical characteristics measurement (Id-Vd, BVdss, capacitance).

- The process flow analysis report estimates the chip manufacturing process based on the results of the structural analysis, includes estimation of process flow, number of masks, cross section of process sequence and the discussion of the relationship between electrical characteristics and psychical structure.

Structure analysis report: \$7,000 / Process analysis report: \$4,600

# **Table of Contents Structure Analysis Report**

|                                                | Page |

|------------------------------------------------|------|

| Device summary                                 |      |

| Table 1, Executive Summary                     | 3    |

| Analysis result summary                        | 4    |

| Table 2. Device structure                      | 5    |

| Table 3. Device cross section                  | 6    |

| Package analysis                               |      |

| Package overview                               | 8    |

| X-ray observation                              | 10   |

| Plane view analysis                            |      |

| Plane view (optical microscope)                | 11   |

| Plane view, Scanning Electron Microscope (SEM) | 23   |

| Cross section analysis (SEM)                   |      |

| Die thickness                                  | 26   |

| Cross section of GaN transistor                | 27   |

| Cross section of die edge                      | 37   |

| Cross section analysis (TEM)                   |      |

| GaN-Epi, Metal layer                           | 42   |

| TEM EDX analysis                               |      |

| GaN-Epi, Metal layer                           | 48   |

| Electrical charcteristic                       |      |

| Ids-Vds (on mode)                              | 62   |

| Id-Vgs                                         | 63   |

| Leakage current (off mode)                     | 64   |

| Break down voltage                             | 65   |

| Cap-Vds                                        | 66   |

## Table of Contents Process Analysis Report

| F                                                                      | Page |

|------------------------------------------------------------------------|------|

| Executive summary                                                      | 3    |

| Device structure                                                       | 5    |

| Discussion device structure and process flow                           | 9    |

| Analysis summary                                                       |      |

| Table 3. Die structure                                                 | 15   |

| Table 4. Each layer material and thickness                             | 16   |

| <u>Process flow</u>                                                    |      |

| Front end wafer process flow (estimation)                              | 17   |

| Process sequence cross section                                         | 18   |

| Electric characteristic                                                |      |

| Comparison with other makers' GaN FET (Data sheet)                     | 23   |

| On-state Id-Vds                                                        | 24   |

| Id-Vgs                                                                 | 25   |

| Off-state leakage current                                              | 26   |

| Breakdown voltage                                                      | 29   |

| Cap-Vds                                                                | 30   |

| Relation between physical structure and electrical characteristic: Ron | 31   |

| <u>Appendix</u>                                                        |      |

| Reference papers list                                                  | 33   |